VHDL

5 bit updown counter

전자자연인

2021. 6. 9. 21:39

반응형

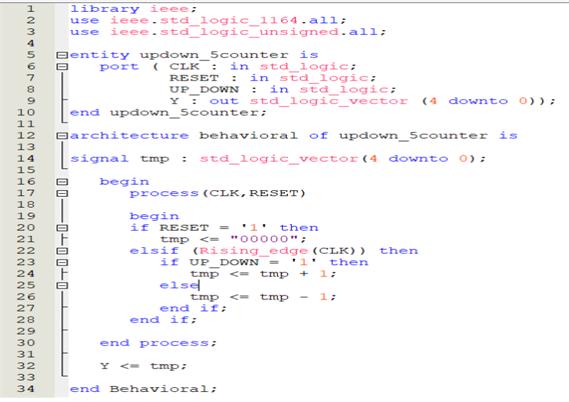

1.5 bit updown counter

5bit로 이루어진 2진수 카운터이다 00000에서 1이증가하면 00001 이 되고, 1이 증가시 00010되고 최고값 11111에서 1이 증가시 00000이 된다. 00000에서 1이 감소하면 11111이된다.

2. 업다운 카운터

14 : inout을 위한 로직벡터 선언(4부터 0까지 내림차순)

17 : CLK,RESET의 PROCESS문 -> CLk RESET에 따라 값이 바뀜

20~22RESET값이 1일 시, 00000이 tmp값으로 전달된다.

23 : CLK신호가 rising edge일 시, 입력신호 UP_DOWN이 1일시 tmp의 신호에 tmp+1값을 전달한다, 다른 경우 tmp 에 tmp-1값을 전달한다.

32 : Y의 tmp에 값을 전달함( Y는 출력 )

3.시뮬레이션 결과 및 설명 <보기쉽게 출력을 OCTAL>

(1) 처음 RESET신호가 1일 시, 출력은 00이된다.

(2) CLK 신호가 Rising edge일 시,UP_DOWN신호가 1이 될 때, 1이 증가한다.

(1) CLK 신호가 Rising edge일 시,UP_DOWN신호가 1이 될 때, 1이 증가한다.

(2) UP_DOWN신호가 0이되고 CLK신호가 Rising_edge일시 1이 감소한다

반응형