반응형

▶Multiplexer - 멀티플렉서(MUX)란 n bit개의 선택선의 조합에 의해 2^n개의 입력선 중에서

하나를 선택하여 출력선에 연결시켜주는 회로이다.

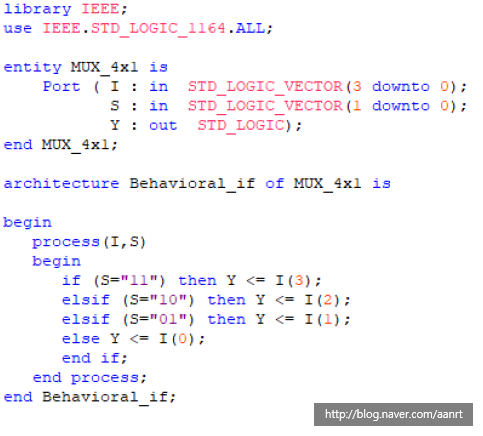

▶4x1 VHDL 동작적모델링 IF문사용

4x1 mux - 동작적모델링(behavioral)으로 if문 사용하여 서술한 VHDL

▶4x1 Mux - dataflow VHDL

dataflow - 논리식을 그대로 대입 (편함)

dataflow - when~else 구문 사용 ( 병행기술문으로 process밖에서 사용 ↔ case~when문은 동작적 모델링으로 process내에서 사용

● dataflow 선택문은 기타조건에서 when others문대신 "11"을 사용해도 되지만, 합성기에 따라 다를 수 있으므로, '-'(don't care)나 null문 사용하면 논리 최적화에 유리하게 만들어주면 좋음!

▶4x1 mux 결과 시뮬레이션

8x1 mux

▶8x1 mux dataflow vhdl

ibrary ieee;

use ieee.std_logic_1164.all;

entity eightMux is -- eightMux에 대한 포트 설정

Port ( I : in std_logic_vector(7 downto 0); -- I는 8비트의 입력로직벡터이나 7부터 0으로 내림차순으로 정렬 I7 I6 I5 I4 I3 I2 I1 I0

S : in std_logic_vector( 2 downto 0); --S는 3비트의 입력로직벡터이나 2부터 0으로 내림차순으로 정렬 S2 S1 S0

Y : out std_logic); -- Y는 출력로직

end eightMux;

architecture Dataflow of eightMux is --eightMux에대한 자료흐름적 구조

begin

Y <= I(7) when S = "111" else

I(6) when S = "110" else

I(5) when S = "101" else

I(4) when S = "100" else

I(3) when S = "011" else

I(2) when S = "010" else

I(1) when S = "001" else

I(0);

end Dataflow;

▶8x1 mux 시뮬레이션

반응형

'VHDL' 카테고리의 다른 글

| 8x3 Encoder , 8x3 엔코더 VHDL (0) | 2021.06.08 |

|---|---|

| 3x8 Decoder 설계 (0) | 2021.06.08 |

| ALU dataflow (0) | 2021.06.08 |

| Demultiplexer(Demux) 1x4,1x8 (0) | 2021.06.08 |

| 조합회로 - 비교기 (자료흐름적 모델링) (0) | 2021.06.08 |