<b> </b>

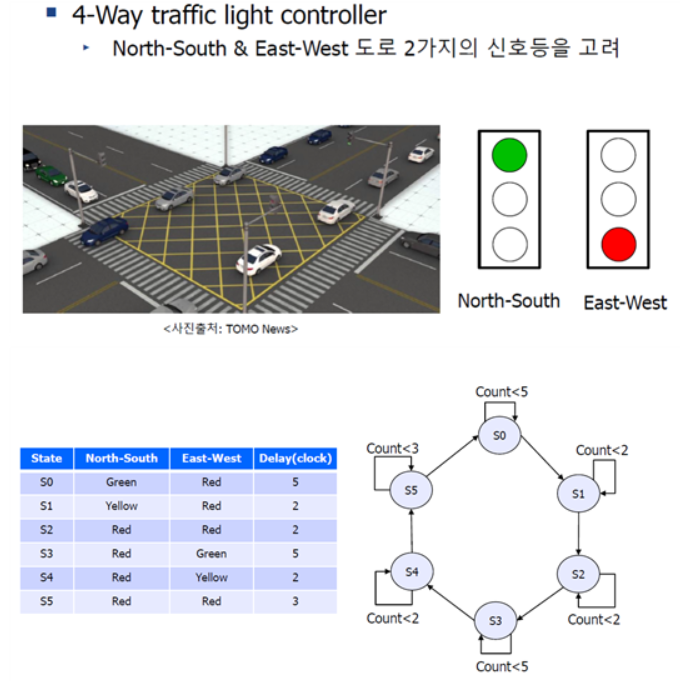

S0에선 북-남쪽이 초록불일 땐, 남북이 통행해야 하므로 동-서 는 빨간불이 되어야 한다

<b> </b>

S1에선 북-남쪽이 황색일 때, 동서는 다음 초록신호를 기다려야 하므로 빨간불이 되어야 한다.

<b> </b>

S2에서 서로 빨간불이 되어 횡단보도(예시)의 신호를 기다린다.

<b> </b>

S3에선 동서쪽이 통행을 해야하므로 북쪽은 빨간색이 되어야한다.

<b> </b>

S4에선 이제 다시 남북쪽이 통행하기위한 중간단계로 동서쪽은 황색불이고 남북은 빨간불이 되어야 한다.

S5에선 다시 서로 빨간불이 되어 다음 남-북의 통행신호가 되기를 기다린다.

2. 소스코드 및 설명

14: state의 type을 정해준다 (내용은 s0,s1,s2,s3,s4,s5)

16~21 : 각 신호에 관한 시간을 상수처리해주어서 선언한다.

23 : 이전과 다음에 관한 state를 signal형으로 선언해준다

24 : time_setting이란 타이밍을 신호로 선언하고 상수형의 0~5범위를 가지는 값을 선언한다.

27:rst과 clk에 관한 출력값을 설정해준다.

28:0부터5까지 정수범위를 가지는 cnt의 변수값을 지정해준다.

30:rst이 1일시 이전상태는 s0을 전달 cnt는0을 대입함.

33:clk신호가 상승신호시마다

34:cnt는 cnt+1 즉,1씩증가하는 값을 대입해준다.

35:clk펄스의 신호에따라 cnt가 증가하며

cnt값이 time_setting의 값과 같아지면

next_state를 전달해주고 cnt는 0으로 초기화한다.

42: pre_state 의 값에 따라 출력이 되는 process문

44: pre_state의 관한 case문

45~50 : s0의 state일 때,

R,Y,G에 해당하는 2비트로직벡터값을 전달해준다.

상수형 정수5를 전달해주고 p1:process문에 의하여 clk펄스가 5번상승(cnt=5)가 되면

next_state에 s1을 전달해준다.

51~80번도 각 state (s1,s2s,3s4,s5)마다 RYG에 출력신호를 전달하고

상태에 맞는 time_setting값에 선언해준 상수형정수의 값을 전달하여 cnt값을 정한다음 cnt값을 초기화 한후 next_state에 다음 stata를 전달해주어 넘어간다.

3.시뮬레이션 및 결과 설명

출력 R,G,Y에 있어서 1비트의 자리는 남북, 0비트의 자리는 동서이다.

1은 점등을 의미하고 0은 소등을 의미한다.

1. rst이 1일시 s0인 상태가 된다. S0은 남북이 초록, 동서는 빨간불이므로 G의 1비트자리에 1이(남북이초록),0비트의 자리에 0(동서는 초록불이안들어옴)이 되고

R은 1비트 자리에 0이(남북은 R에 점등이안됨), 0비트 자리에1 0(동서는 R에 점등) 이 된다. 5clock동안 유지된다.

2. 1번의 s0상태가 clk pulse의 5clock동안 유지되고 다음에 s1의 상태가된다.

s1상태는 남북은 Yellow, 동서는 Red이므로 , Y는 10 (남북 점등,동서 소등)가 되고 G는 둘 다 소등, R은 동서만 점등이므로 01이 유지된다. 2clock동안 유지된다

3. S1에서 2clock 후 S2로 변하므로 S2에선 동서남북이 모두 빨간불 이므로,

R는 11, G,Y는 00이 된다. 2clock동안 유지된 후 다음 S3로 넘어간다.

4. S3에선 동서가 통행이므로 G의 0비트자리가 1이되고,

남북은 통행할수 없으므로 빨간불 R의 1비트자리가 1이된다.

G = 01, R=10, Y=00이 출력 된다. 5clock동안 유지후 다음 상태로 넘어간다.

'VHDL' 카테고리의 다른 글

| Coffe Vending Machine 설계(Meerly) (0) | 2021.06.09 |

|---|---|

| Coffe Vending Machine VHDL (Moore설계) (0) | 2021.06.09 |

| Sequence Detector(순차검출기) (0) | 2021.06.09 |

| 램메모리 VHDL RAM(Random Access Memory) VHDL (0) | 2021.06.09 |

| ROM memory (Read Only Memory) VHDL (0) | 2021.06.09 |