반응형

순차회로 COUNTER 설계

1. 비동기식 카운터

● 비동기식 카운터는 리플 카운터라고도 하며, 기본구성은 JK FF을 일렬로 연결 또는 T FF일렬로 연결 -> 토글(toggle 반전)기능 활용

-> JK FF사용 : 모든 J,K 입력 1 / T FF사용 : T입력 1

● 이전 FF의 출력을 다음 FF에 트리거, 다른 FF는 각 FF의 출력을 다음 FF의 ClockPulse입력으로 사용

4 BIT Asynchronous UP Counter ( JK FF )

4비트로 이루어진 비동기식 업카운터이다. JK FF 4개로 이루어져 있으며

초기화값을 0000으로 주어 CLOCK PULSE(falling edge)에따라 1씩 증가하는 카운터이다.

비동기식 증가형 카운터는 동기식처럼 클럭을 공통으로 사용하지 않고 앞쪽에 있는 플립플롭의 출력이 뒤쪽에 있는 플립플롭의 클럭으로 사용된다. 위 회로는 상승모서리 트리거 방식이므로 클럭이 0에서 1로 올라가는 순간 동작하게 된다.

2. 4 BIT Asynchronous UP Counter Schematic

Vcc는 J,K에 항상 1을 넣어주기 위함이다. (J,K 둘다 1일시 toggle이용)

초기값이 0000이라 가정 하였을 때,

(1) 클럭이 입력되면 첫 번째 JK플립플롭이 0, 1을 반복하게 된다. 두 번째 플립플롭은 첫 번째 플립플롭의 출력 Q가 1에서 0이 되는 순간 클럭이 입력되어 동작하게 된다.

(2) 위 회로는 하강모서리에서 동작하므로 클럭신호가falling edge순간("1"에서 "0"이된는 순간) 첫 번째 플립플롭이 동작하고 나머지 플립플롭은 전단의 출력 Q가 1에서 0으로 되는 순간 동작하게 된다.

(1) 결과를 보면 REST이 1일 때, 0000으로 초기화가 되고

클럭신호의 falling_edge(1에서 0이되는 순간) Q0에 0이입력되어 1이출력되고 Q1에 Q0의 출력값의 not (=0)이 클럭신호로 들어가 내부동작을 하지않게된다

(2) 그다음 clock pulse에서 다시 falling_edge순간 Q0의 1이 0으로되고 Q1의 신호에 1이 출력되고 Q3엔 Q2의 출력값의 not이들어가므로 (=0) 작동하지않게되어

다음 신호는 0010이 출력된다.

(3) 0010에서 다음 clock pulse에서 falling edge순간 0비트의 0은 1이되고 1비트부터 3비트까진 작동하지 않으므로 0011이 출력된다.

1. 4비트 비동기 다운 카운터 4 bit asynchronous down counter

클럭이 입력되면 첫 번째 JK플립플롭이 0, 1을 반복하게 된다. 두 번째 플립플롭은 첫 번째 플립플롭의 출력 Q'가 0에서 1이 되는 순간 클럭이 입력되어 동작하게 된다.

상승신호(Rising edge)에서 동작하므로 Clock Pulse가 High되는 순간에("0"에서 "1"이된는 순간) 첫 번째 플립플롭이 동작하고 나머지 플립플롭은 전단의 출력 Q'가 0에서 1로 되는 순간 동작하게 된다.

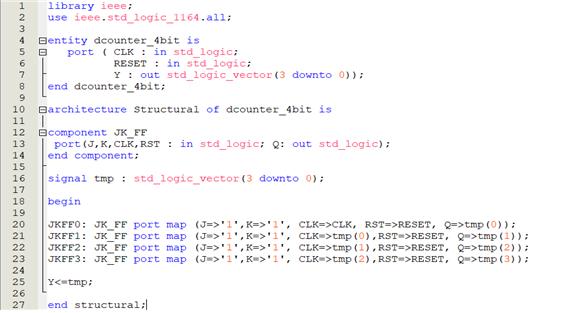

4~8 : entity dcounter_4bit의 포트 선언 CLK클락신호,RESET리셋신호,Y출력신호

10 : 설계한 JKFF을 사용하기위한 구조적모델링의 dcounter_4bit 아키텍쳐

12~14 : 사용할 JK_FF의 component를 사용하여 port 입출력 설정

16 : inout형을 대신하기 위한 signal tmp(3부터0내림차순) 선언 (쿼터스에서 inout시 오류확률 높아)

20 JKFF단계 : 설계한 JK_FF에 J,K는 항상1을 전달해고 JK_FF의 CLK,RST,Q신호를 dcounter_4bit의 CLK,RESET,tmp(0)의 값으로 차례대로 전달해줌

21 JK_FF1단계 : 설계한 JK_FF의 CLK,RST,Q의 신호를 dcounter_4bit의 tmp(0),RESET,tmp(1)로 차례대로 전달해줌

22 JK_FF1단계 : 설계한 JK_FF의 CLK,RST,Q의 신호를 dcounter_4bit의 tmp(1),RESET,tmp(2)로 차례대로 전달해줌

23 JK_FF1단계 : 설계한 JK_FF의 CLK,RST,Q의 신호를 dcounter_4bit의 tmp(2),RESET,tmp(3)로 차례대로 전달해줌

여기서 Q는 JK_FF의 출력값이고 각비트의 Q출력값을 tmp(0,1,2,3)로 전달한다

25 : dcounter_4bit의 출력logic Y의 값에 tmp값을 전달해준다.

<항상 J,K는 1신호를 준다.>

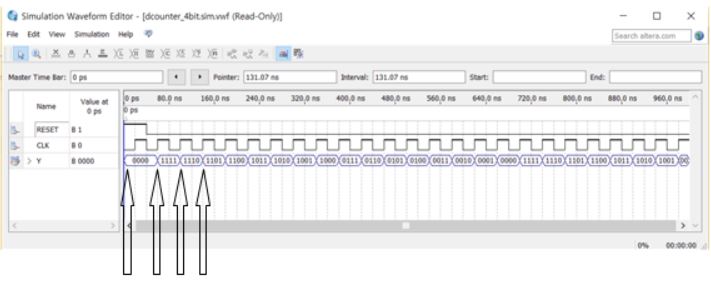

(1) 처음 입력신호에 RESET 신호가 1이 됫으므로 모든 출력값은 0000이된다.

(2) 다음 Clock Pulse의 상승 rising edge일시 모든값이 토글되므로 초기값은 1111이된다.

(3) 다음 Clock Pulse의 상승 rising edge일시 0비트의 값이 반전되고 0비트의 값의 반전된 값이 1비트의 CLK입력신호로 들어간다. 그래서 내부동작을 안하게되어 1110이 된다.

(4) 똑같은 동작으로 0비트의 값이 반전되고 1비트의 값이 반전되고 1비트의 출력값이 반전되어 2비트로 들어가 내부동작을 하지않게되어 1101출력된다.

반응형

'VHDL' 카테고리의 다른 글

| 모듈로 10 UP-DOWN-COUNTER (0) | 2021.06.09 |

|---|---|

| 5 bit updown counter (0) | 2021.06.09 |

| Shift Register(쉬프트 레지스터) VHDL (0) | 2021.06.08 |

| FND DECODER ( DE2보드) (0) | 2021.06.08 |

| 8x3 Encoder , 8x3 엔코더 VHDL (0) | 2021.06.08 |